Fsm2s

From HDLBits

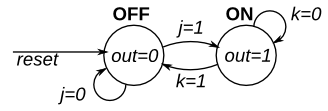

This is a Moore state machine with two states, two inputs, and one output. Implement this state machine.

This exercise is the same as fsm2, but using synchronous reset.

Module Declaration

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out);