Fsm1

From HDLBits

conwaylifePrevious

Nextfsm1s

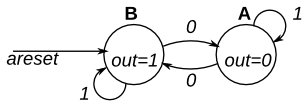

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1s, but using asynchronous reset.

Module Declaration

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);

conwaylifePrevious

Nextfsm1s