Srlatch

From HDLBits

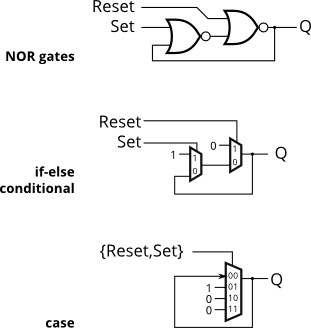

A SR latch is a circuit with memory (remembers its old state) that can be Set or Reset by the control inputs. There are many ways to code this, including building it from NOR gates, if-else, or a case statement in a combinational always block.

In the diagrams, the reset input has higher priority than the set input. Build a SR latch where the set input has higher priority.

In this exercise, all of the inputs and outputs are active high.

I've removed this problem from the problem set. SR latches are not always synthesized correctly, depending on coding style. Writing an SR latch is not suitable when you don't have the post-synthesis netlist to verify the output of logic synthesis, nor those new to Verilog and not yet familiar with how logic synthesis tools can synthesize incorrect circuits.

Details: If the logic synthesizer interprets the code as a D-latch + logic, you get:

Enable = set | reset;

Q = Enable ? set : Q;

This produces a non-working latch because the Enable and D inputs change at the same time.

Module Declaration

module top_module (

input set,

input reset,

output q );